White Paper posted on Oct 8, 2017

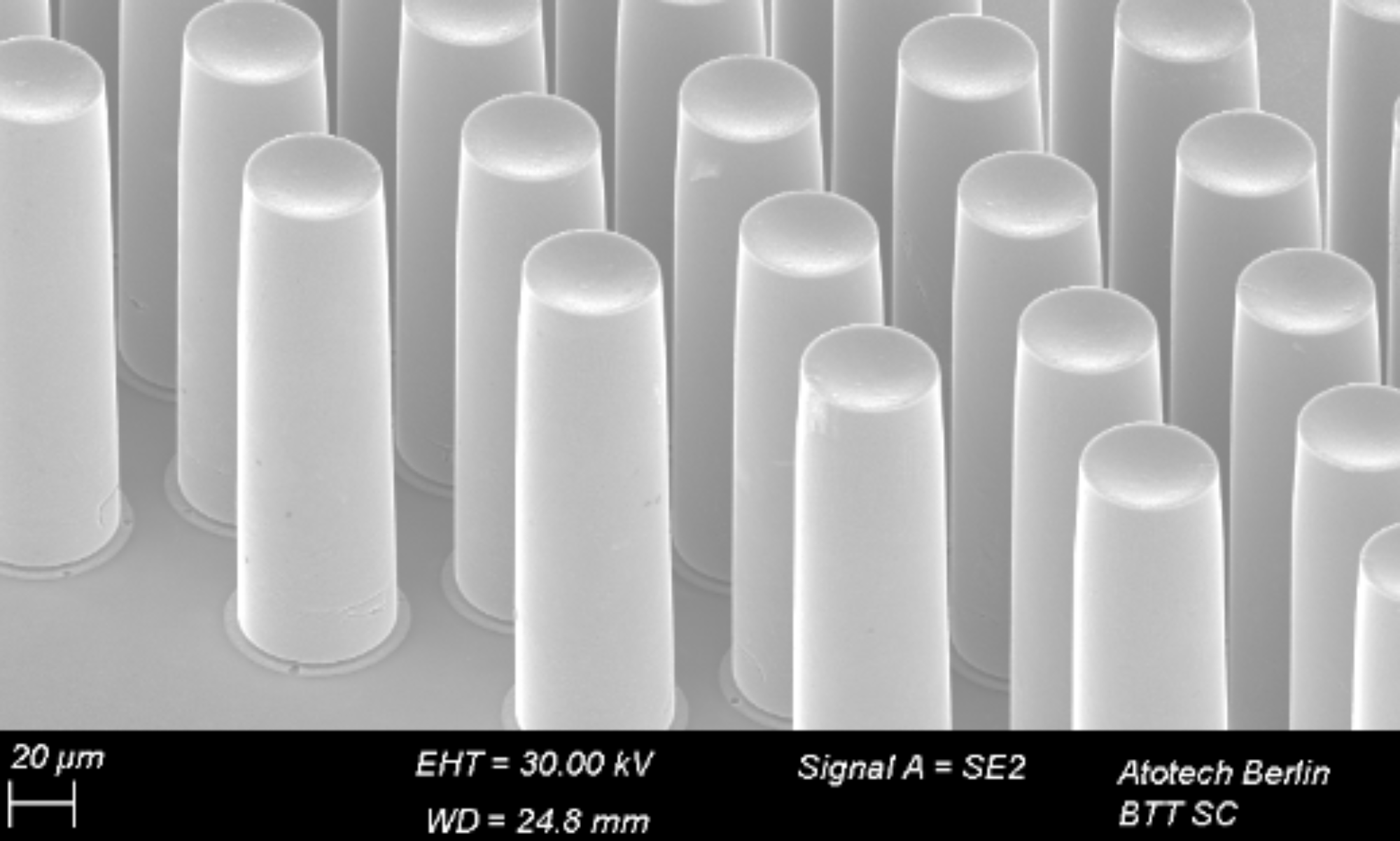

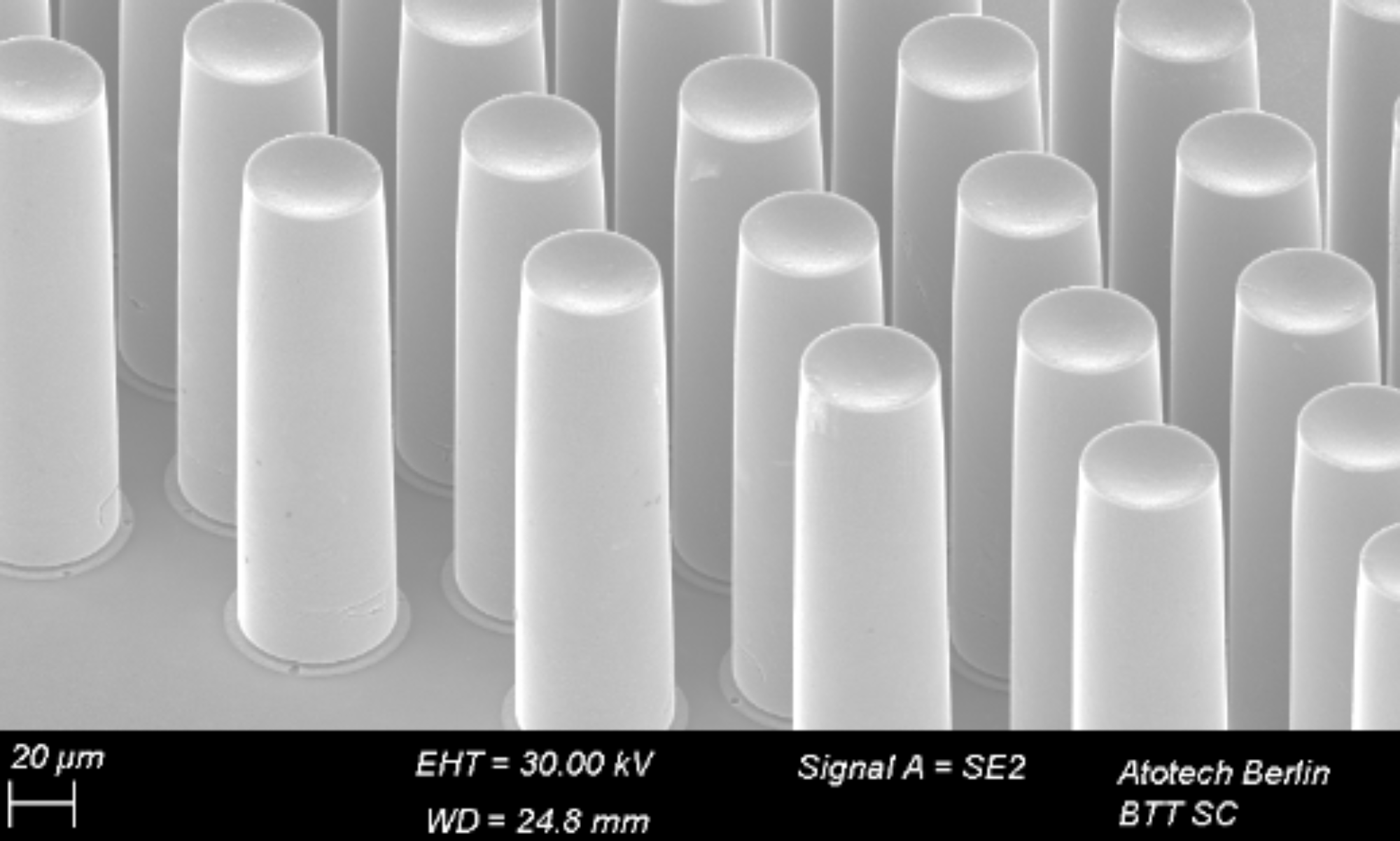

With demands for shrinking footprints and increasing I/O of electronic components, there is an increasing interest in electrodeposited Cu pillar structures for Package on Package (PoP) interconnects. One example of interest involves a 3D package integration approach with the memory mounted above the processor for mobile applications. This paper will explore the processes required and discuss the challenges for Cu pillar fabrication of PoP interconnects at sub 100um pitches. The test vehicles will include variables such as pillar diameter and pitch for a 200um thick liquid film negative tone plating resist on a 300mm wafer format. The high-density pillar pitch is expected to present challenges to resist material applications, lithography capability, and plating capability. Work for this paper is supported by major material and tool suppliers for resist materials, lithography tools, and plating chemistries & plating tools