Article posted on Jun 12, 2019

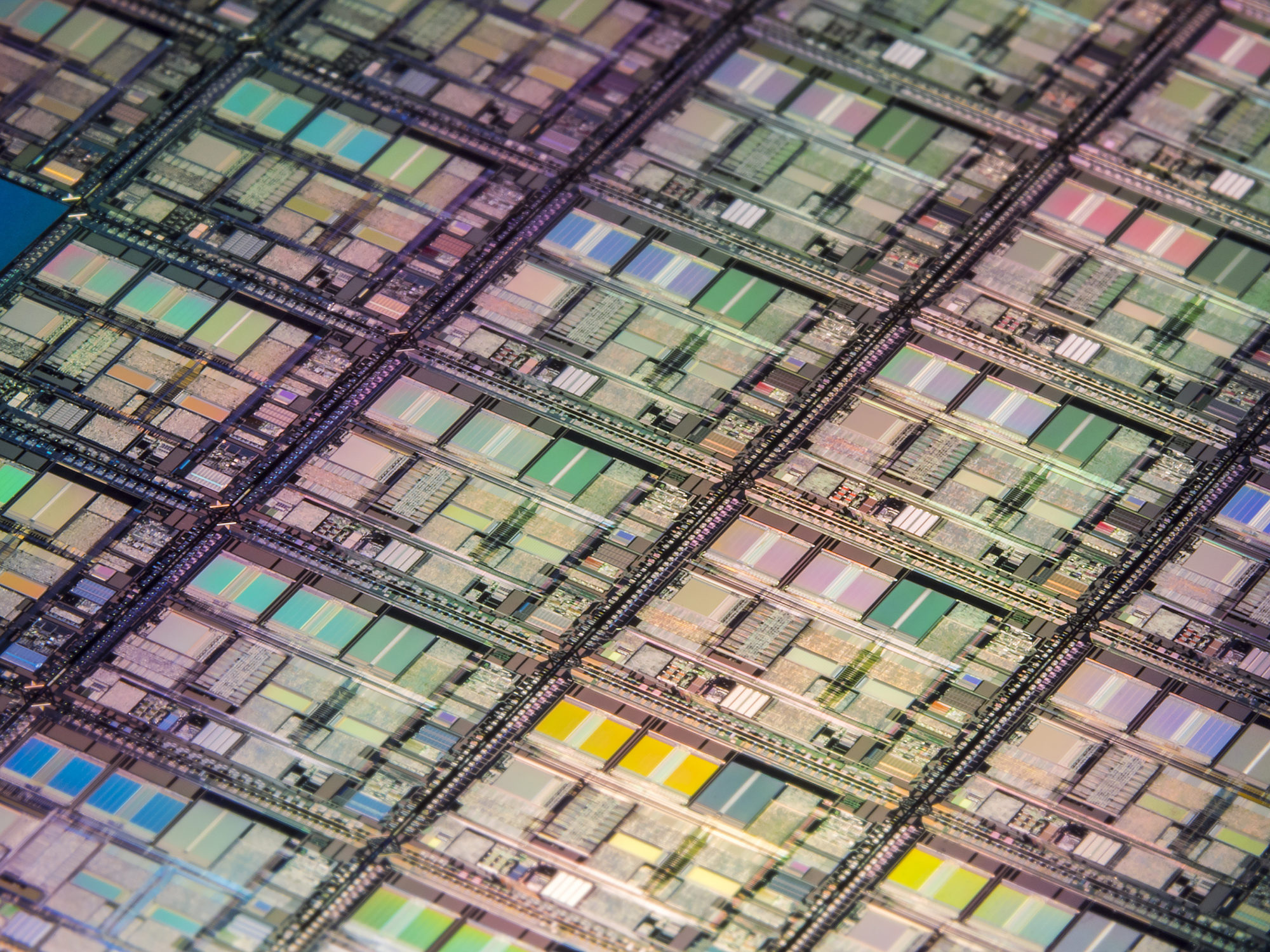

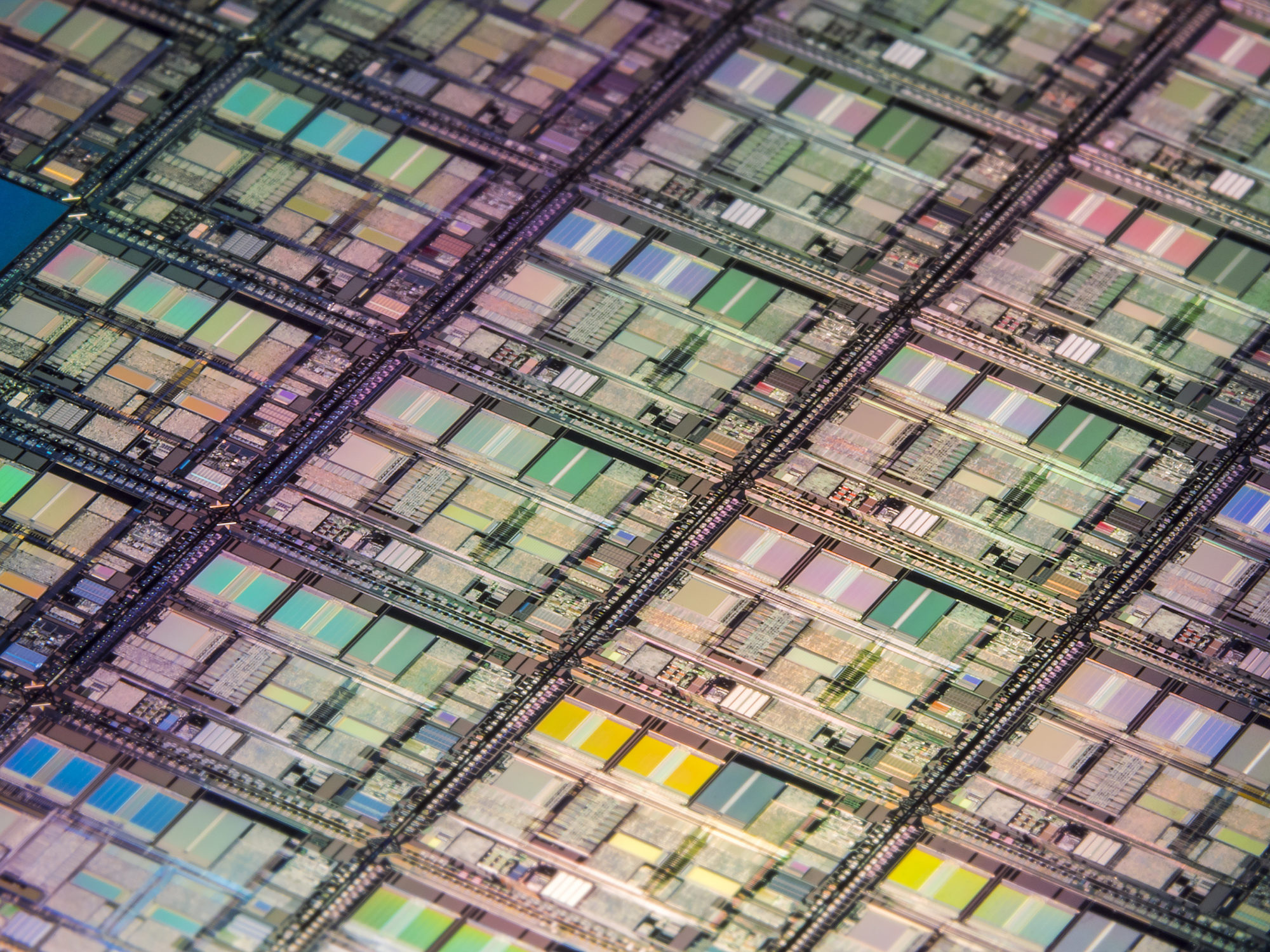

While wire bonding remains the dominant technology for chip-to-package connections, advanced packaging processes are gaining a growing share of the market. The transition away from wire bonding is especially notable in high-performance memory applications, where shorter signal paths, higher speed, smaller form factor and lower power are most valuable. Significant growth is forecast for both flip-chip dynamic random access memory (DRAM) and high-bandwidth memory (HBM) across a broad range of applications, with a commensurate decrease in wire bonding. Flip-chip, wafer-level packaging (WLP), fan-out wafer-level packaging (FOWLP), and fan-out panel-level packaging (FOPLP) are now seeing increasing adoption. These advanced packaging methodologies present unique inspection and metrology challenges and opportunities, including through-silicon vias (TSVs), fine-pitch redistribution layers (RDLs), copper pillar bumps, micro-bumps and die-level cracks.

Although advanced packaging technologies generally use more front-end-like processes, they include many structures not used in most front-end applications, including TSVs, RDLs, pillars, micro-bumps, and solder bumps. These are inherently three dimensional and all bring inspection and measurement requirements that are unique to advanced packaging processes.

Metrology and inspection systems for advanced packaging processes have often adapted technologies used in traditional front-end or back-end applications, but some critical applications have required the development of new sensors and techniques, including: high-speed laser triangulation for whole-wafer bump height metrology and advanced white light and infrared interferometry for measurements of film thickness, optical profiling, substrate metrology, and via and carrier trench depth metrology. Additionally, there are new non-visual defects that traditional inspection technologies have not been able to detect. These defects may be invisible cracks or residues that may not be caught during electrical test but cause reliability issues downstream. In this case, the development of laser-based contrast inspection has provided much needed defect detection capability.